Matrix Multiplication Labview Fpga

I know that we can use linear algebra matrix multiply function but I have trouble implementing it and the help page is not very useful. Matrix multiplication on FPGA has been discussed in PowerDev forum.

Transferring Multi Channel Data In Dma Applications Fpga Module Labview 2018 Fpga Module Help National Instruments

AbstractThis paper describes an FPGA design that performs 4x4 matrix multiplication.

Matrix multiplication labview fpga. Traditional methods used approaches such as VHDL b. The design was done by the five authors over a span of approximately 3 weeks though of the 15. When you wire matrix data as an input to this function a VI that includes subVIs that work with the matrix data type replaces the function.

VHDL code for Matrix multiplication is presented. Input pattern of BSpecifies that the function receives data from matrix B element by element in the matrix by vector by row-wise or by column-wise. Anyone have any experience with this and can share an example VIimage.

The core is implemented on Xilinx FPGA Spartan-6 XC6SLX45-CSG324-3. Download this and checkout IP CoresIP Cores - LabVIEW FPGAHIL SolverMatrix Multipy A x X - 9 x 9 - Marcusvi which is an example for a 9x9 matrix multiplication. Hey guys Quite new to LabVIEW and FPGA architecture.

I am trying to create a 4x4 matrix multiplication in the FPGA space that is have a 4x4 input matrix A and multiply it by 4x4 input matrix B and give a resulting 4x4 matrix as C. I have completed a few of the courses labview 123 realtime. Hey guys Quite new to LabVIEW and FPGA architecture.

If I have to multiply more than 2 complex vector in a single clock would it be possible. The function performs per-element multiplication and multiplies the elements in one array by the corresponding elements in the other array. We define fn as the total number of arithmetic operations required.

Therefore fn n3 n2 n 1 2n3 - n2 The complexity is of On3. Therefore providing a fast speed implementation using CPU GPU or FPGA has always been a challenge. Matrix multiplication is one of the operators that have a wide range of applications in image processing scientific computing simulation robotics and so on.

Matrix-matrix multiplication in such a way that it is split between the FPGA and PowerPC on a Xilinx Virtex IIPro 30. Here I briefly explain how to implement this operator on FPGA. The Multiply function performs simple multiplication not matrix multiplication.

The node remains a VI if you disconnect the matrix from. In this paper we discuss our solution which we im-plemented on a Xilinx XUP development board with 256 MB of DRAM. This VHDL project is aimed to develop and implement a synthesizable matrix multiplier core which is able to perform matrix calculation for matrices with the size of 32x32.

I am trying to create a 4x4 matrix multiplication in the FPGA space that is have a 4x4 input matrix A and multiply it by 4x4 input matrix B and give a resulting 4x4 matrix as C. In an ideal hardware implementation of matrix multiplication all of the multiplications. Fractional binary numbers fixed point notation binary multiplication matrix addition and fetch routine.

The resulting VI has the same icon but contains a matrix-specific algorithm. Keywords-sparse matrix vector multiplication FPGA accelerator SPMV SMVM reconfigurable computing HPC I. Each component of the matrices is 16-bit unsigned integer.

Refer to the A x B VI for more information about matrix multiplication. The module only supports multiplication of scalars. Editing the IP for a 4x4 might take a bit of work but shouldnt be too complicated for engineering minded LabVIEW developers.

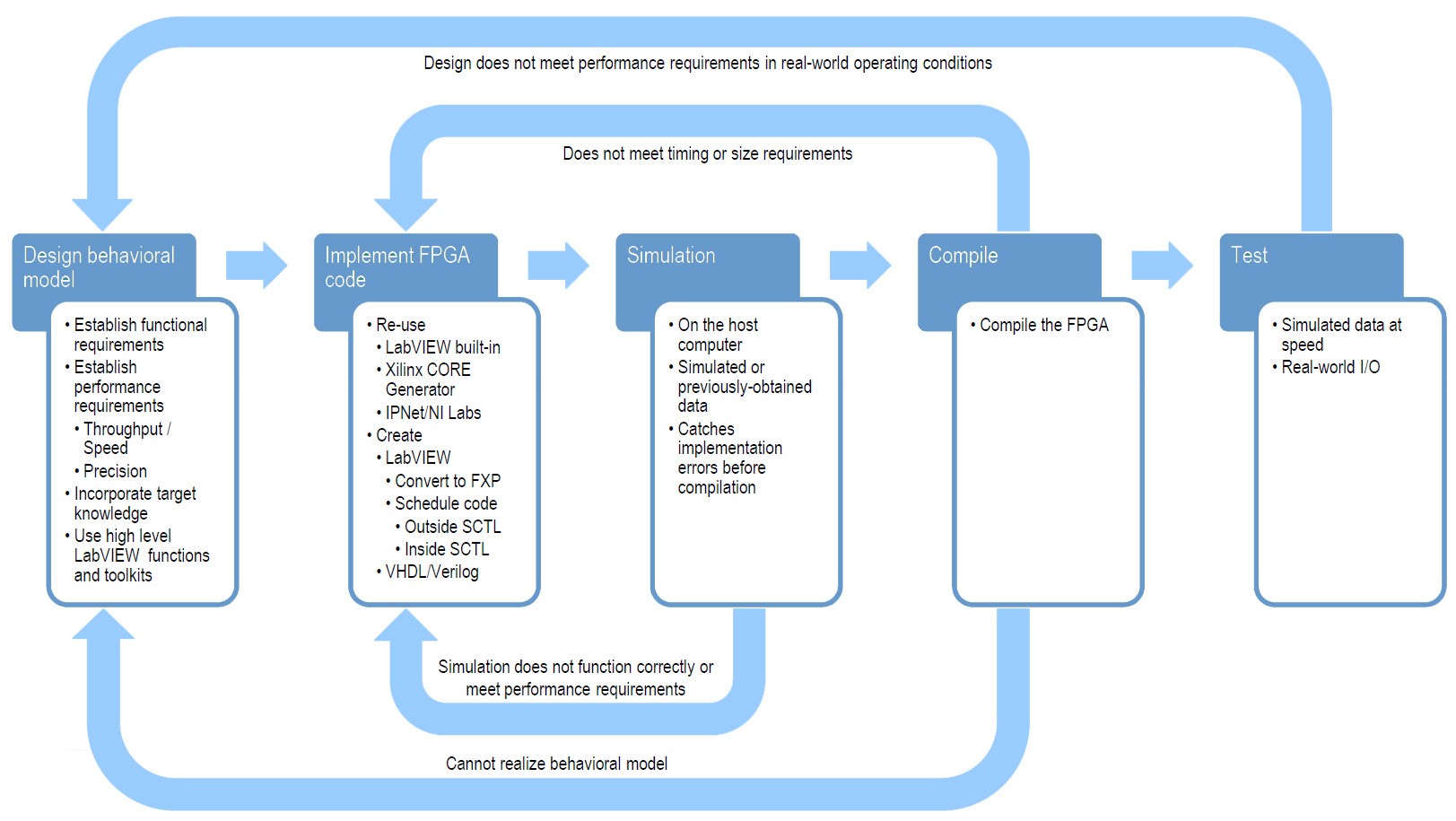

The goal of the design is to optimize throughput area and accuracy. I am not expecting any answers like. Knowing how to programme an FPGA is one of the key steps to the successful implementation of FPGA designs.

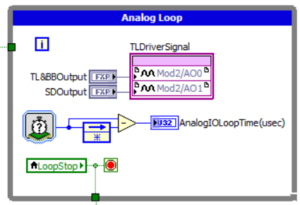

LabVIEW calculates the Throughput of this function based on the values of M L and N as specified in Matrix Size. My understanding is to use Complex Multiplier. Matrix multiplication in LabVIEW FPGA module.

But that is to multiply only 2 complex vectors. Matrix multiplication requires n3 multiplications and n2 n 1 additions. Cck_n_codeexp 1jPhi1cck_encoding_table index1.

My question how to model Matrix Multiplication with Complex Vectors. For example if the first element of array A is 4 and the first element of array B is 2 wiring these two arrays to the Multiply function results in an array. The design of our matrix multiplier consists of four main parts.

INTRODUCTION Sparse matrix-vector multiplication SMVM has received significant attention due to its increasingly important application in scientific and commercial applications eg computational fluid dynamics computer. I have completed a few of the courses labview. Selecting fewer cycles per matrix results in a higher throughput rate.

Sve što trebate znati o dijetama i mršavljenju.

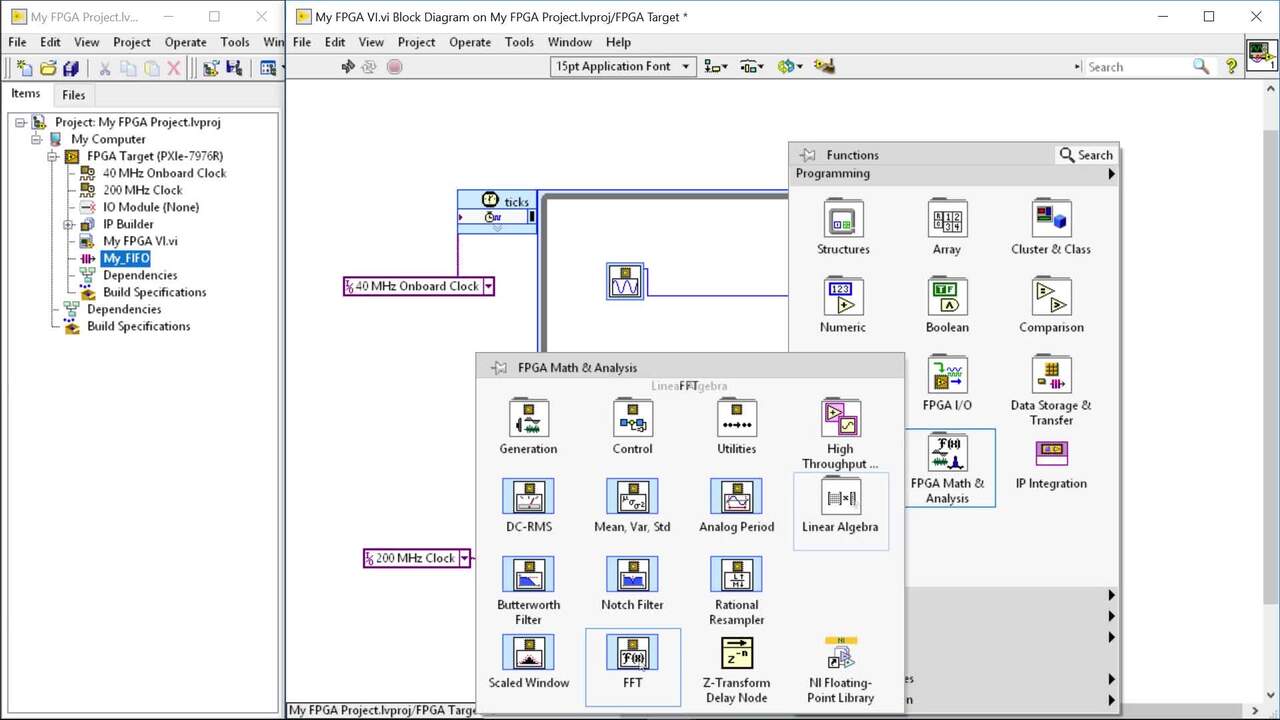

Labview Fpga Math And Signal Processing Palette Each Subpalette Download Scientific Diagram

Introduction To Fpga Vision Using The Ni Labview Fpga Module Automation World

Standalone Fpga Acquisition Module Implementation And Integration With Download Scientific Diagram

.png)

What S The Labview Fpga Learn It Now Technical Articles

Fpga Ip Builder Tutorial Fpga Ip Builder Labview 2018 Fpga Module Help National Instruments

An Introduction To High Throughput Dsp In Labview Fpga Ni

Labview Uses What Is Labview Used For 4 Purposes

Standalone Fpga Acquisition Module Implementation And Integration With Download Scientific Diagram

Filtering Fpga I O Using Multiple Input Channels Fpga Module Labview 2018 Fpga Module Help National Instruments

Implementation Of Eigen Decomposition In Labview Fpga Download Scientific Diagram

Implementation Of Eigen Decomposition In Labview Fpga Download Scientific Diagram

Taking Your First Measurement In Labview Fpga Data Logging National Instruments

Pass Array Between Fpga Loops Ni Community

What Is The Labview Fpga Module Ni

Using Pid On Fpga Targets Labview 2018 Help National Instruments

Tip Ffts In Labview Fpga Ee Times

Designing Fixed Point Multirate Filters Digital Filter Design Toolkit Labview Digital Filter Design Toolkit Documentation

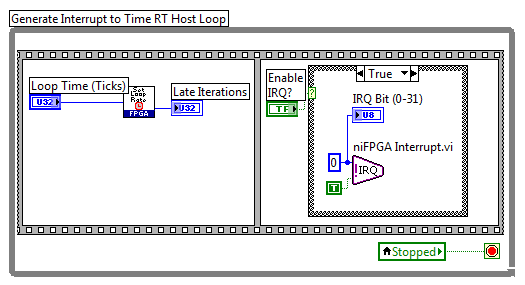

Adding Personality To Veristand Fpga Eehelp Com